What’s Affected by PDN Impedance?

The impedance of your PDN is the main driver of power stability on your design, and high PDN impedance is a root cause of unstable power in your design. While any type of design can have power integrity problems, where the desired voltage seen at the IC is disturbed during operation, we usually like to talk about digital systems when discussing PDN impedance and power integrity rather than analog systems. Larger, faster ICs with high I/O count, high data rate capability, and fast rise time are prime candidates for power integrity problems, but even small microcontrollers can have the same types of issues with power integrity.

In particular, there are three interrelated power integrity problems that arise from having high PDN, high inductance along signal return paths, and fast switching currents in the design:

- Supply bounce: Although not the most-often used term, this refers to the transient voltage fluctuation on the power bus, which is then telegraphed to load components on each branch of the PDN.

- Ground bounce: This refers to a transient oscillation seen on the output from a switching signal. This is sometimes confused with crosstalk as it appears on the output signal from fast digital components during switching.

- Jitter Jitter occurs due to fluctuations in the nonlinear capacitance of transistors that make up logic circuits.

What is so interesting about these three effects is that they are interrelated nonlinearly, and you can develop a nonlinear causal stability model to describe the transition between equilibria when a switching event occurs. In addition, they are all related to the PDN impedance in some way.

Supply Bounce vs. Ground Bounce

If you’re reading the above description and you’re thinking "this sounds a lot like ground bounce", then that’s understandable. Ground bounce and supply bounce have the same root cause: excessive inductance somewhere in the PDN. The difference is in location. The diagram below shows the major contributors to ground bounce and the effects of ground bounce as seen in a pair of CMOS buffer circuits. The resulting ringing is shown schematically in the inset graph.

Parasitics in the package and board layout (L and C elements) create an LC circuit along the signal path. This induces a transient oscillation measured between the I/O pin and GND, which is superimposed on the equilibrium I/O voltage.

With ground bounce, also known as simultaneous switching noise, the origin of the problem is inductance along the path followed by signals that are output from CMOS buffers, which creates a transient oscillation that is superimposed on the output from the circuit. When the driving CMOS buffer switches, the resulting inrush or discharge of current encounters several sources of inductance and capacitance. These include via inductance, the I/O pad capacitance, load capacitance, plane inductance, and any parasitics on the bypass capacitors used to suppress ground bounce. Like it or not, bypass capacitors are still part of the PDN and will still see the PDN impedance; it’s this input switching action among multiple buffers that drives ground bounce to be seen on the output signal.

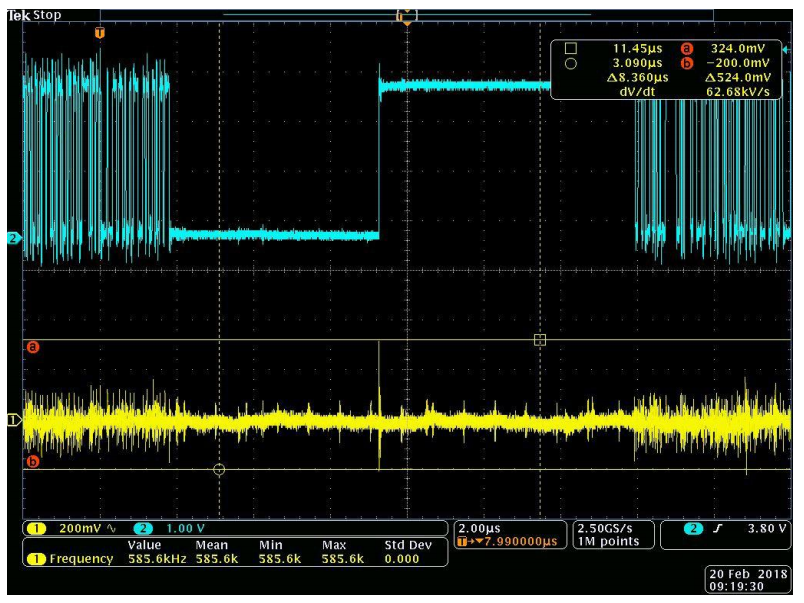

With supply bounce, inductance is also a problem, but it’s the inductance along the power rail leading to the supply, as well as parasitic inductance in decoupling capacitors. Supply bounce is the voltage fluctuation measured between the VCC port and GND on the driving CMOS buffer. Contrast this with ground bounce, which is measured between the I/O pin on the driver and GND. Both effects will be present when a digital circuit has insufficient bypassing/decoupling; the example oscilloscope trace below nicely shows the two effects occurring simultaneously, as can be seen when the I/O switches (blue trace).

Ground bounce (blue) and supply bounce (yellow) traces on an oscilloscope.

Jitter

Jitter arises due to fluctuations in triggering instance of FETs that make up CMOS logic circuits. This could be due to variations in capacitance at terminals, variations in the trigger time of an upstream circuit, and variations in the current pulled into a logic circuit from VCC/VDD. Where do these capacitance fluctuations come from? Again, the root cause is the PDN impedance and the voltage ripple that can arise when PDN impedance is too high. When the power ripple reaches the input rail on the IC, the ripple modulates the body capacitance in the MOSFET. By modulating this capacitance, the circuit’s rise and fall time experiences fluctuations that are a nonlinear function of the voltage ripple measured on the power rail.

Testing for Power Integrity Problems Due to PDN Impedance

Functional testing is an important part of the prototyping process, and PDN impedance is one of the important points to evaluate in the PCB layout. If you’ve produced a test board for measuring parasitics in the PDN, you can use a VNA to calculate the PDN impedance (Z-parameters) from an S-parameter measurement. Impedance matching at the measurement ports in your VNA is extremely important; the reference impedance is normally set to 50 Ohms by default, while the PDN impedance is on the order of mOhms. Such a large mismatch can produce very large errors when gathering an S-parameter measurement for the PDN.

For supply bounce and ground bounce, you can measure a prototype while in operation with probes. During board bringup and testing, you’ll be able to see power bus ringing on an oscilloscope by measuring the magnetic field emitted from the power rail with a low inductance near-field probe. Make sure to set the right attenuation ratio and matching for your probe to ensure you’re capturing noise produced by ground bounce and ringing, rather than spurious RF fields or some other phantom noise source.

Finally, jitter is best measured with an oscilloscope on a test board by capturing an eye diagram. Your signaling standard will generally list some acceptable limits on eye opening and jitter to ensure the received signal latches to the correct logic state, or that equalization in the receiver can properly recover the signal. You’ll never be able to totally eliminate jitter or other SI/PI problems in your digital systems, but if you’re knowledgeable about how to floorplan your design, you’ll be able to produce a working device that can pass standards testing.